Im Frühsommer stellte SiFive mit den P550 die vorläufig schnellsten RISC-V-Kerne vor. Davon war offenbar auch Intel überzeugt und bietet schon bald entsprechende Designs Kunden des Intel Foundry Services (IFS) an. Bereits 2022 will Intel mit der Horse -Creek-RISC-V-Entwicklungsplattform einen Prozess anbieten, der Kerne, bzw. Cluster und ganze SoCs wie den P550 in 7 nm fertigen lässt.

Im Frühsommer stellte SiFive mit den P550 die vorläufig schnellsten RISC-V-Kerne vor. Davon war offenbar auch Intel überzeugt und bietet schon bald entsprechende Designs Kunden des Intel Foundry Services (IFS) an. Bereits 2022 will Intel mit der Horse -Creek-RISC-V-Entwicklungsplattform einen Prozess anbieten, der Kerne, bzw. Cluster und ganze SoCs wie den P550 in 7 nm fertigen lässt.

Auf der Linley-Konferenz sprach der Vizepräsident von SiFive Shubu Mukherjee nun bereits über den Nachfolger. Erst auf dem RISC-V Summit im Dezember wird es allerdings weitere Details geben.

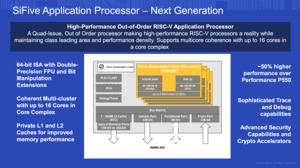

Aber kommen wir zu dem, das SiFive nun präsentiert hat. Der noch namenlose Kern soll um 50 % schneller als der P550 sein. Es handelt sich um einen 64-Bit-Kern mit einer FPU für doppelte Genauigkeit (FP64) sowie mit privatem L1- und L2-Cache. Die P550-Kerne werden in Vierkern-Clustern zusammengefasst und greifen auf einen gemeinsamen L3-Cache mit einer Kapazität von 4 MB zurück. Im ersten Quartal 2022 sollen die ersten Kunden ihre Chips auf Basis des P550 aus der Fertigung bekommen (Tape Out).

| P550 | Next-Gen P-Series | |

| L1-Instruction-Cache | 32 kB | 64 - 128 kB |

| L1-Data-Cache | 32 kB | 64 - 128 kB |

| L2-Cache | 256 kB | bis zu 2 MB |

| L3-Cache | 1 - 4 MB | 1 - 16 MB |

| Core Complex | bis zu 4 Kerne | bis zu 16 |

| Memory Ports | 1x 128 oder 256 Bit | 4x 128 oder 256 Bit |

Der Nachfolger des P550 wird vor allem in der Skalierung breiter aufgestellt. Hier kommen in einem Cluster bis zu 16 Kerne zum Einsatz. Dementsprechend wird der gemeinsame L3-Cache auf bis zu 16 MB vergrößert. Der für die einzelnen Kerne exklusive L2-Cache kann nun bis zu 2 MB groß werden. Schlussendlich werden der der Instruction- und Data-Cache bis zu 128 kB groß – also bis zu viermal so groß. Am eigentlichen Aufbau der Kerne, bzw. der verwendeten Recheneinheiten und der Tatsache, dass es sich um eine 13-Stufen tiefe Pipeline mit Triple Issue im Out-of-Order-Design handelt, tut sich offenbar nichts. Aber Details dazu werden wir auf dem RISC-V Summit erfahren.

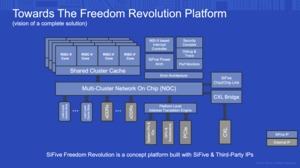

Über die Möglichkeit, mehrere dieser Cluster miteinander zu verbinden, kann ein Design mit 128 Kernen und mehr realisiert werden. Neben den CPU-Clustern können Sicherheitskomponenten, ein großer Last Level Cache und eine Translation Engine mittels Network on Chip (NOC) miteinander verbunden werden. Daraus werden durchaus komplexe Chips mit mehreren (LP)DDR-Speicherkanälen, zahlreichen PCIe-Controllern und Lanes sowie per SiFive Chip2Chip-Link auch einer externen CXL-Anbindung.

Auch wenn RISC-V-Kerne bereits in zahlreichen Chips zum Einsatz kommen, steht der Durchbruch dieser Kerne noch aus. IP-Anbieter wie SiFive arbeiten derzeit offenbar recht erfolgreich daran, das Thema RISC-V weiter auszubauen. Die European Processor Initiative (EPI) arbeitet an Beschleunigern auf Basis von RISC-V, die für den in Europa entwickelten Supercomputer zum Einsatz kommen sollen.

An dieser Stelle wollen wir noch auf unseren Test des SiFive HiFive Unmatched verweisen. Dabei handelt es sich um eine Entwicklerplattform für RISC-V.

https://ift.tt/3B1TyOn

Wissenschaft & Technik

Bagikan Berita Ini

0 Response to "SiFive gibt Vorschau auf den Nachfolger des RISC-V-P550-Kerns - Hardwareluxx - HardwareLuxx"

Post a Comment