Eventuell ein Ausblick auf das Hopper-Design für Supercomputer: Nvidia zeigt, wie sich zwei Ansätze auf einem Package vereinen lassen.

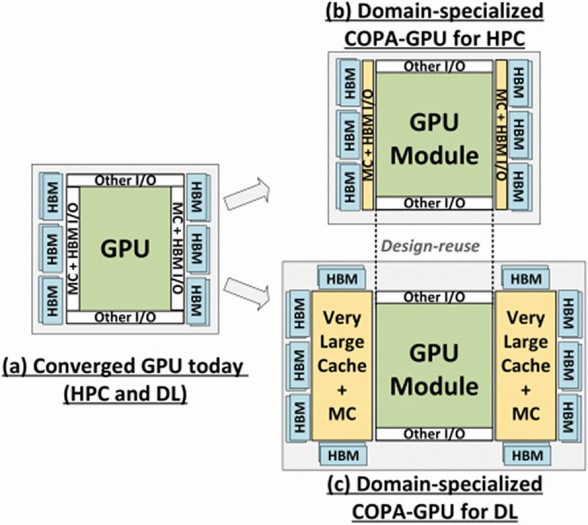

Nvidia hat eine Forschungsarbeit veröffentlicht, die sich um die sogenannte Composable On-Package Architecture für GPUs dreht: Damit wird ein Ansatz umschrieben, bei dem statt eines monolitischen Grafikchips mehrere zum Einsatz kommen, wobei jeder auf bestimmte Berechnungen spezialisiert ist und bessere Resultate erreichen soll.

Heutige Modelle wie der GA100 für etwa die A100-Beschleuniger vereinen diverse Funktionsblöcke wie maschinelles Lernen und das Rechnen mit doppelter Genauigkeit, was einen Balanceakt für die vorhandenen Ressourcen darstellt. Mit einem MCM-Design lassen sich diese aufteilen und optimieren, wie Nvidias Paper aufzeigt.

Die Composable On Package (COPA) genannte GPU-Idee integriert einen DL- und einen HPC-Komplex auf einem Träger, beide mit ihrem eigenen Speicher. Für Deep Learning liegt der Fokus auf INT4/INT8 und FP16, bei High Performance Computing auf FP64 mit großen sowie schnellen Caches für eine möglichst hohe Datenlokalität.

Schneller und günstiger, aber aufwendiges Packaging

Laut Nvidia soll so die Performance beim Training von neuronalen Netzen um 31 Prozent und beim Inferencing, also dem Anwenden dieser Netze, um 34 Prozent verglichen zu herkömmlichen Lösungen steigen. Als beste Variante sieht der Hersteller eine COPA-GPU an, die mit satten 960 MByte an L3-Cache (per eigenem Chip) ausgestattet ist und externen HBM-Stapelspeicher mit 4,5 TByte/s nutzt. Noch mehr L3 und die Bandbreiten skalieren kaum.

Der Vorteil einer Chiplet-Lösung liegt darin, dass zwar der Package-Aufwand steigt, die Kosten für kleine Dies aber geringer sind als für monströse monolitische Chips. Nvidias GA100 liegt mit 826 mm² nur wenig unter dem Limit der Fertigungsmaske (Reticle) von 858 mm², was die Ausbeute (Yield) reduziert. Für das auf die Ampere-Generation folgende Hopper-Design wird daher ein Chiplet-Aufbau erwartet, die Vorstellung könnte auf der GTC 2022 im März erfolgen.

AMD hat mit der Instinct MI250X bereits einen Chiplet-Beschleuniger im Portfolio, die beiden Aldebaran-Dies sind allerdings identisch aufgebaut. Die aufaddierte FP64-Rechenleistung von rund 96 Teraflops bei 3,28 TByte/s Bandbreite ist dennoch enorm, wenngleich die zwei Chips untereinander nur mit 400 GByte/s per Infinity Fabric kommunizieren können.

https://ift.tt/3qVu6Hs

Wissenschaft & Technik

Bagikan Berita Ini

0 Response to "COPA-GPU: Nvidia-Beschleuniger kombiniert AI- und HPC-Chiplets - Golem.de - Golem.de"

Post a Comment